| CSC373/406: 6 [6/13] |    |

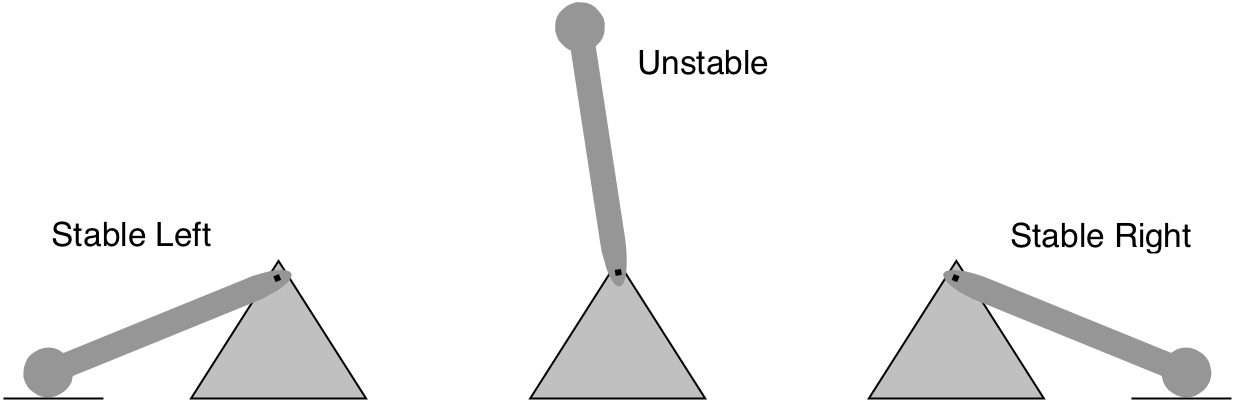

Figure 6.1: Inverted pendulum.

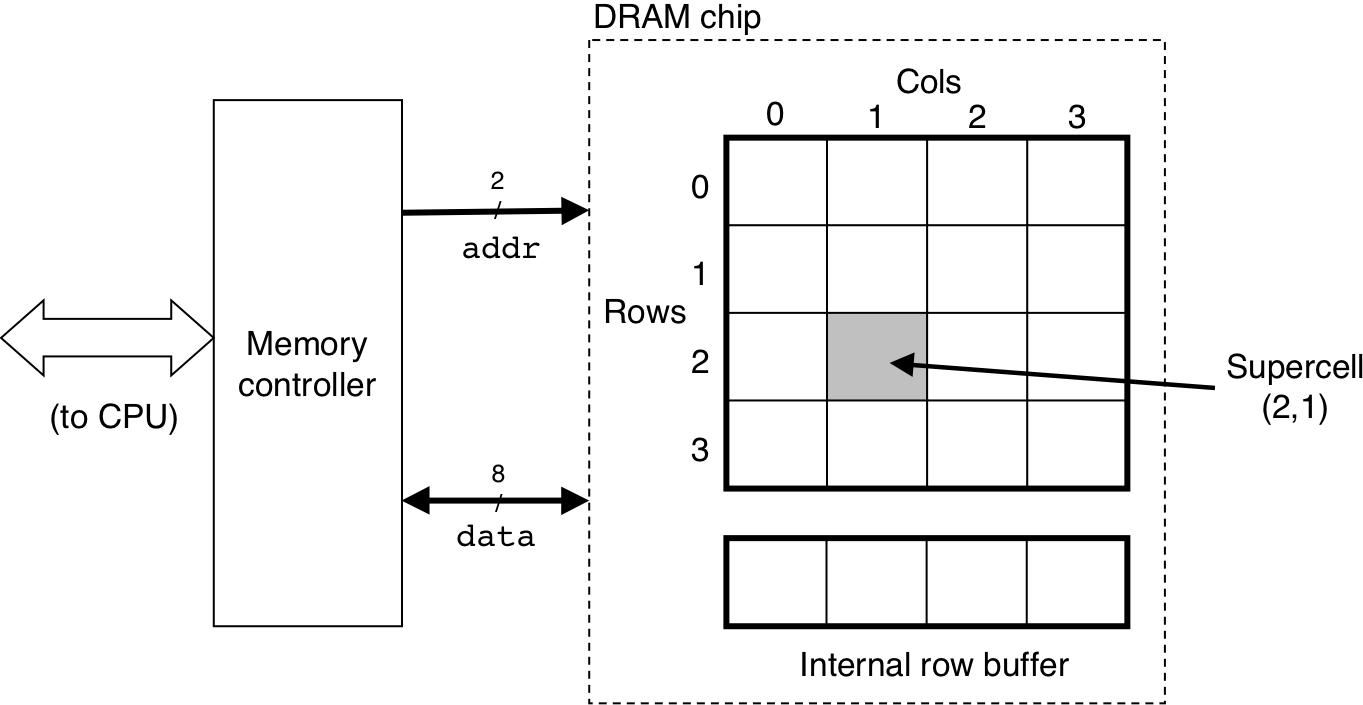

Figure 6.3: High level view of a 128-bit 16 x 8 DRAM chip.

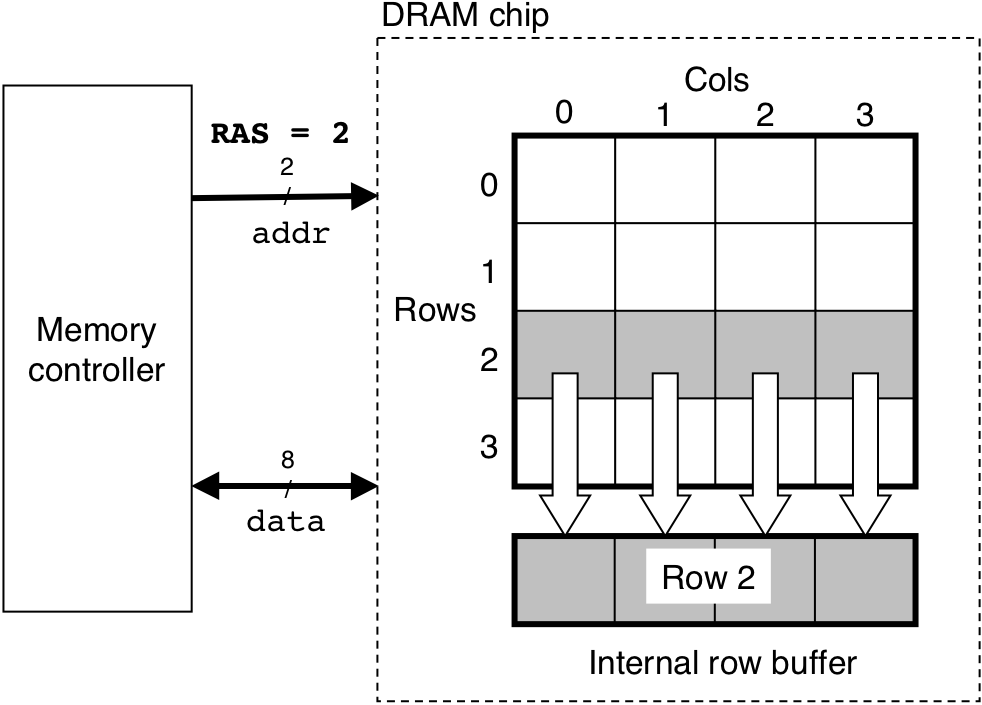

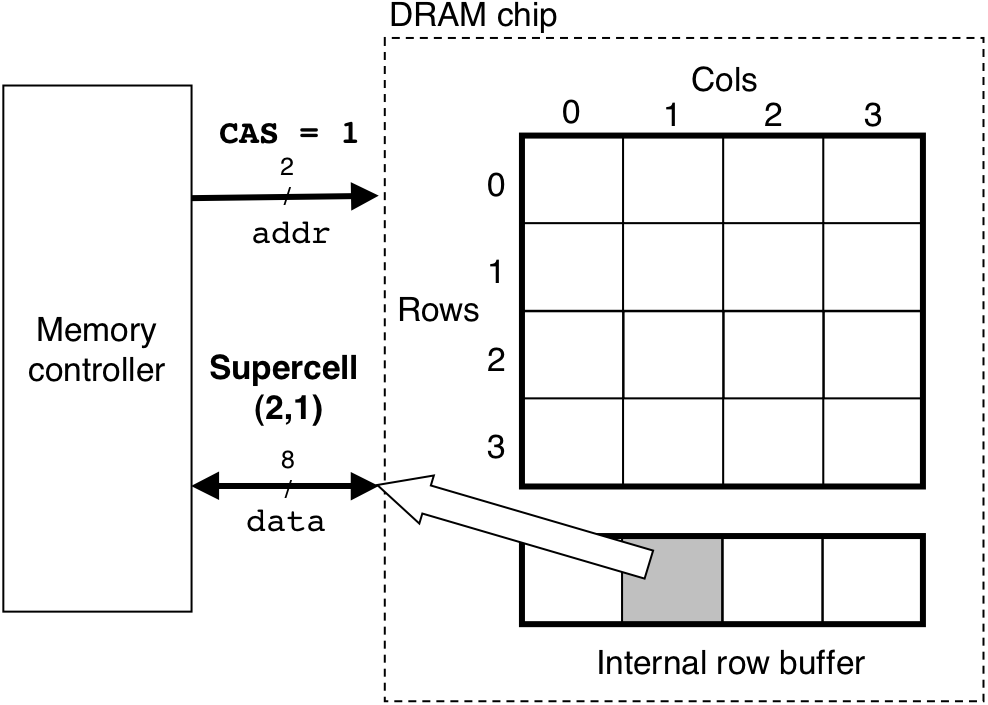

Figure 6.4: Reading the contents of a DRAM supercell.

Figure 6.4: Reading the contents of a DRAM supercell.

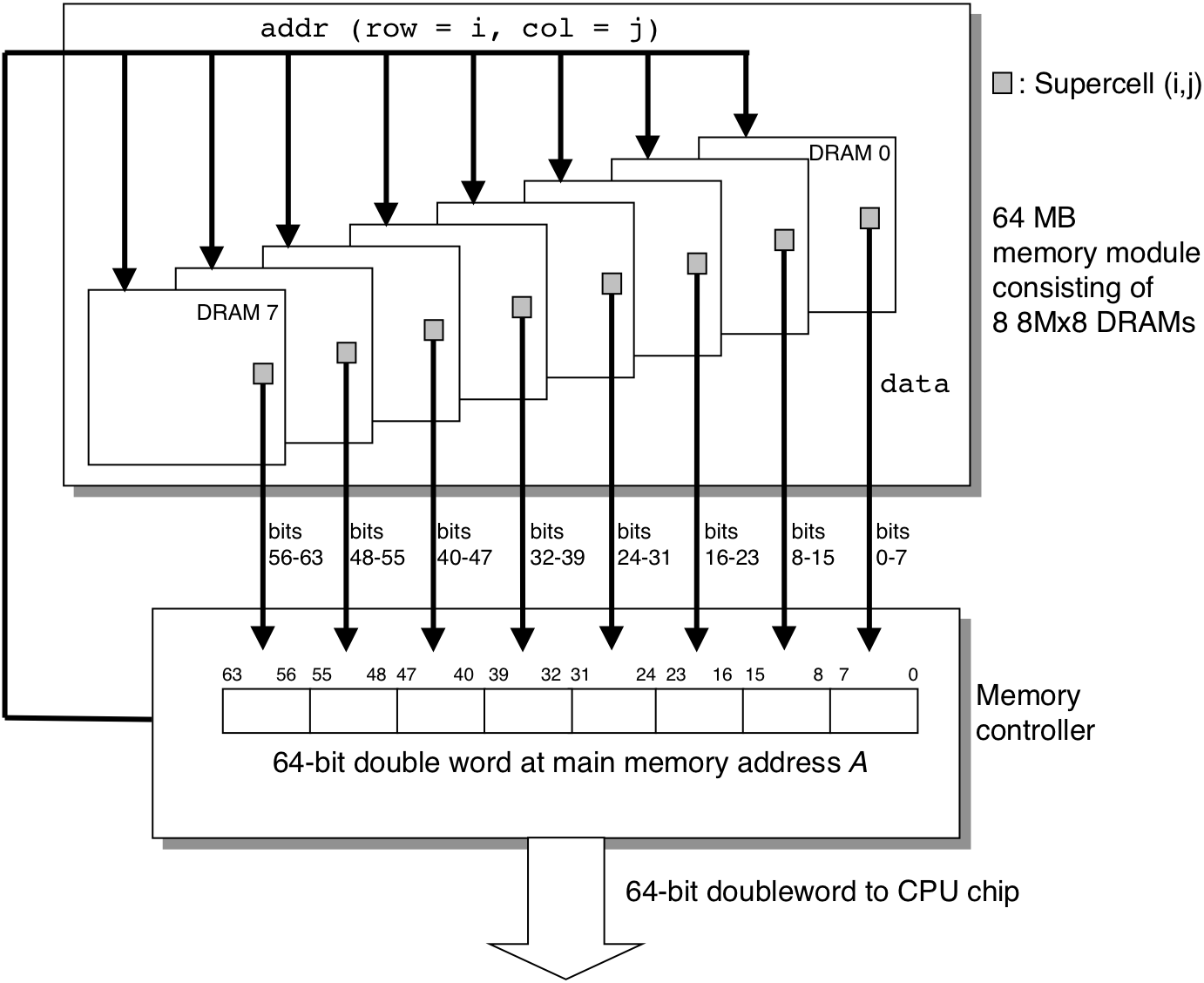

Figure 6.5: Reading the contents of a memory module.

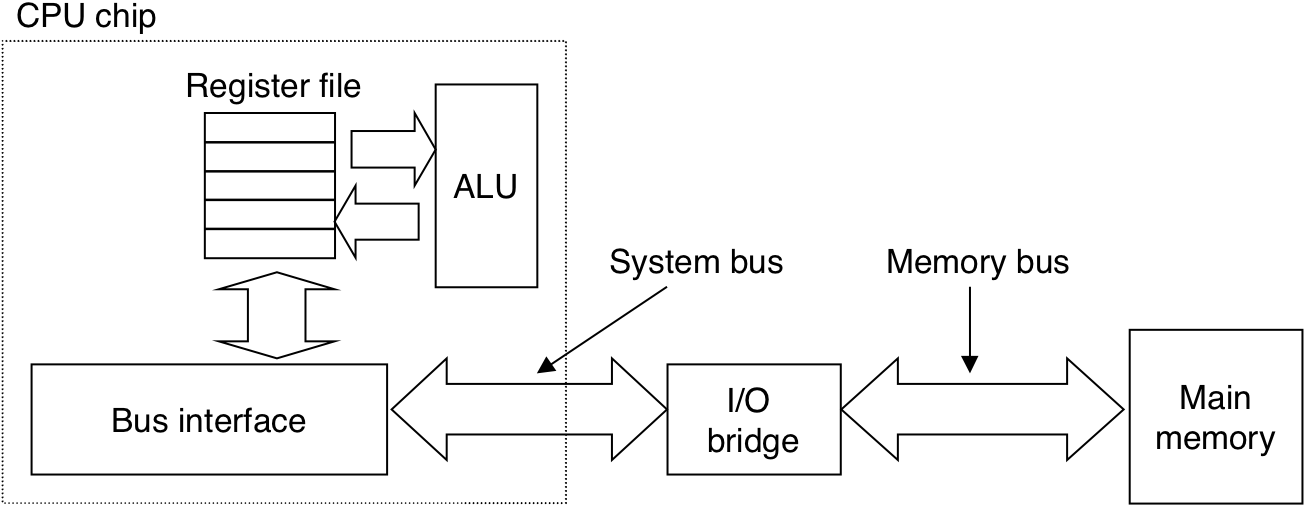

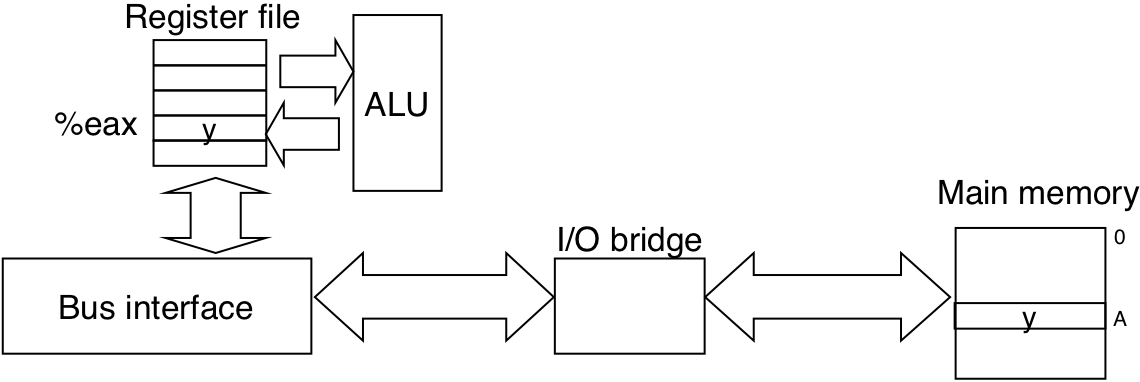

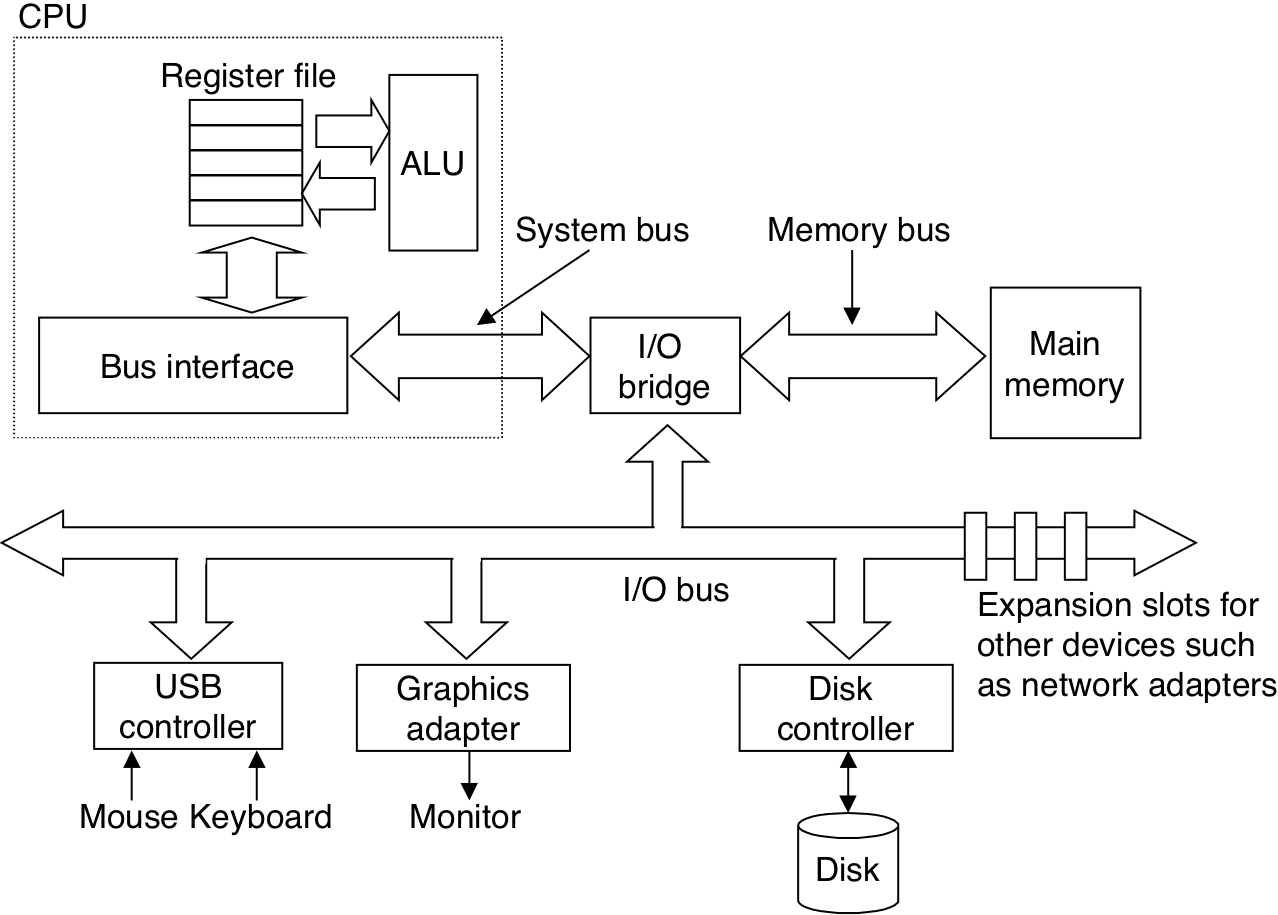

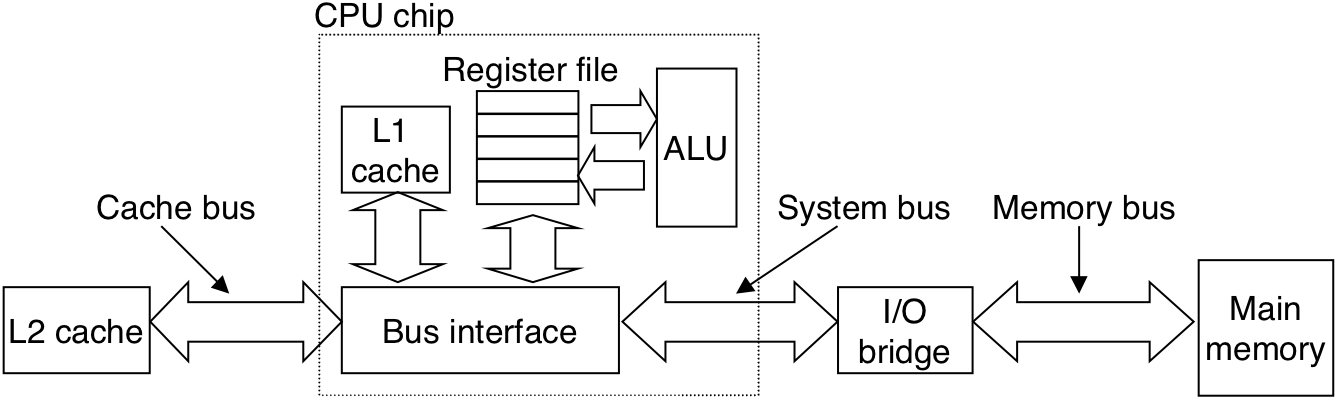

Figure 6.6: Typical bus structure that connects the CPU and main memory.

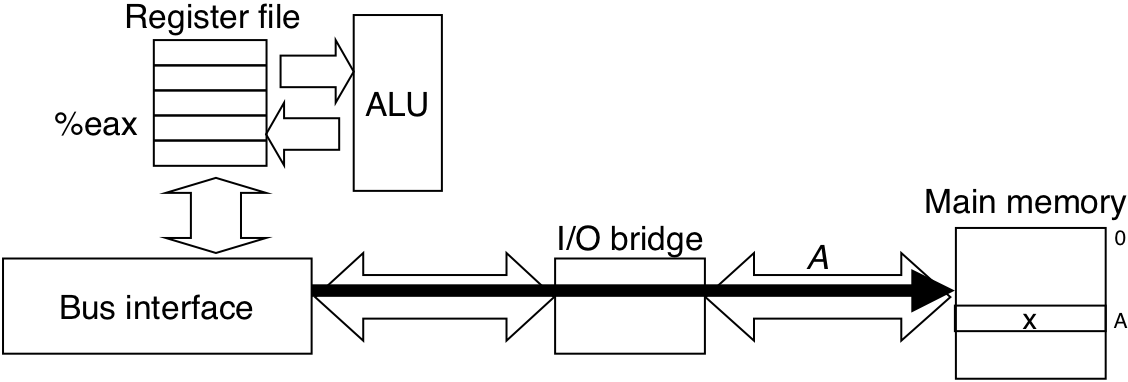

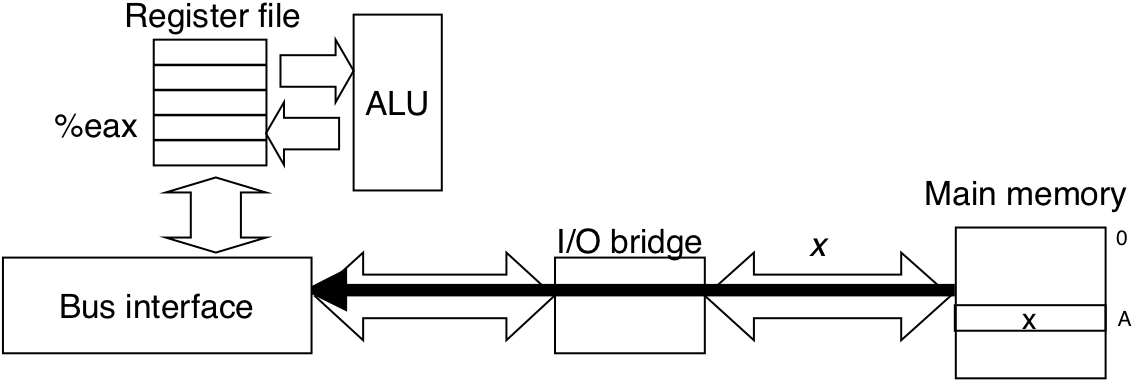

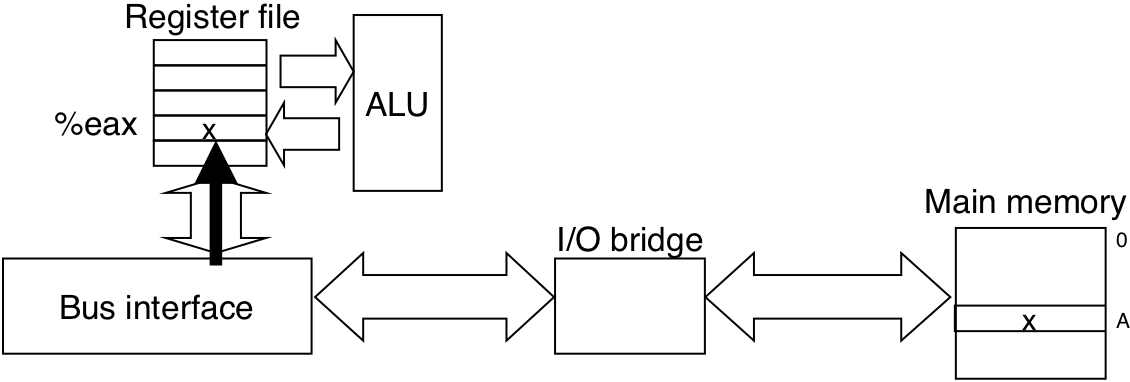

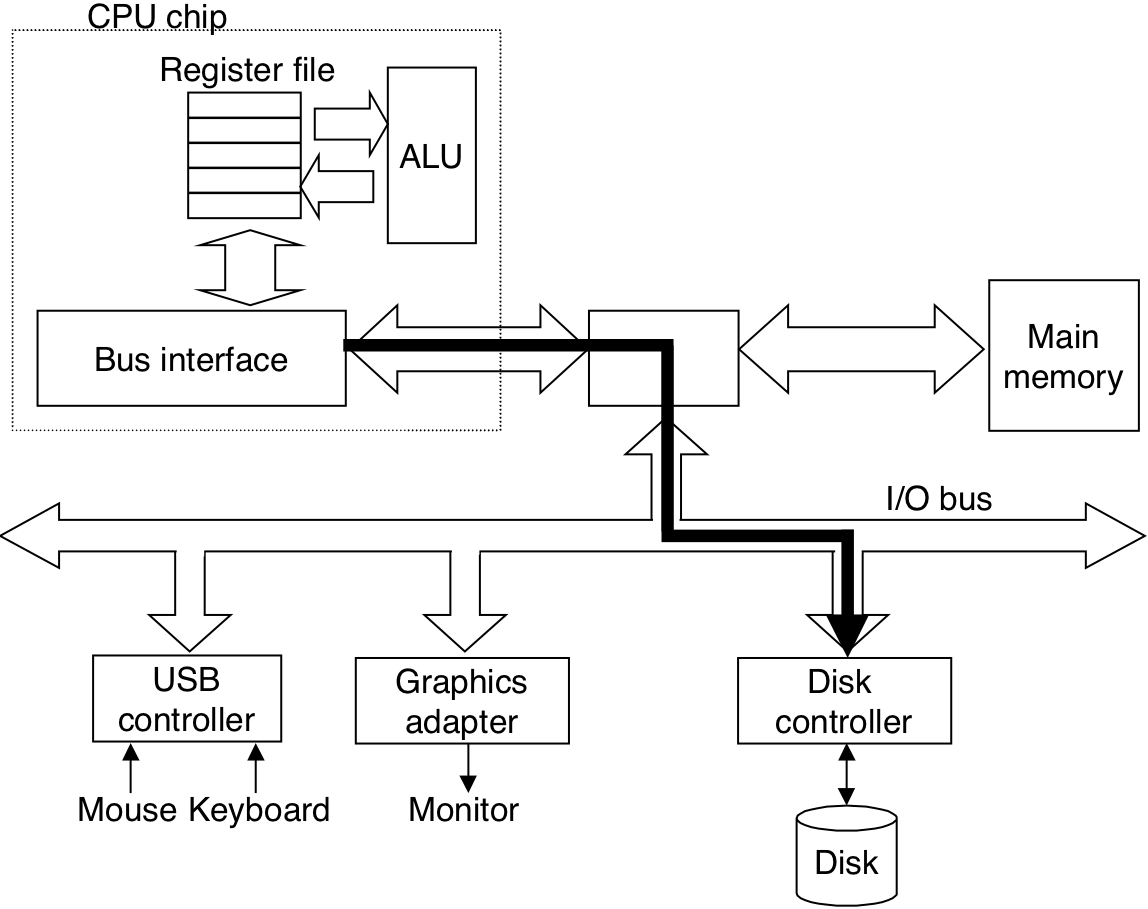

Figure 6.7: Memory read transaction for a load operation: movl A,%eax.

Figure 6.7: Memory read transaction for a load operation: movl A,%eax.

Figure 6.7: Memory read transaction for a load operation: movl A,%eax.

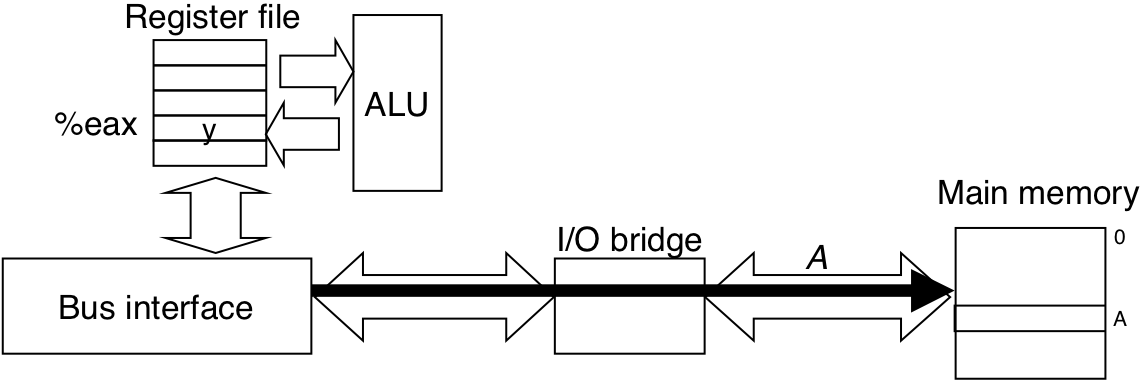

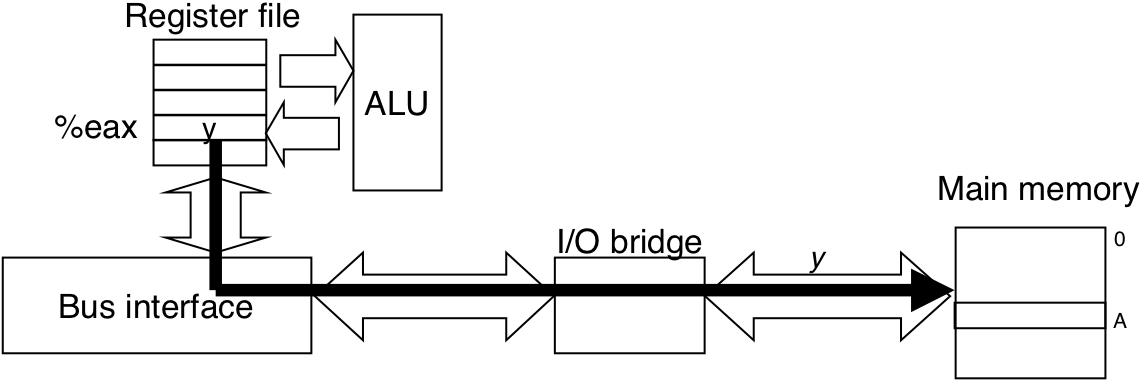

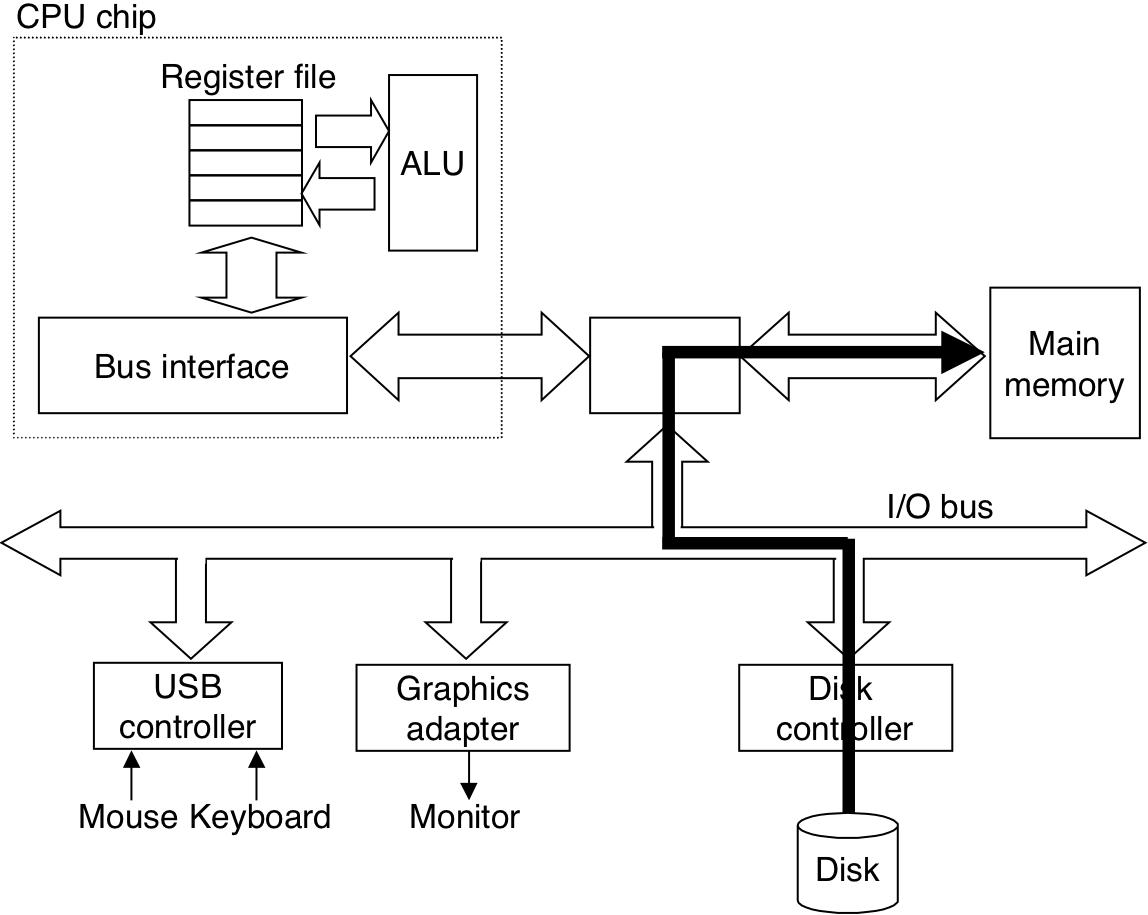

Figure 6.8: Memory write transaction for a store operation: movl %eax,A.

Figure 6.8: Memory write transaction for a store operation: movl %eax,A.

Figure 6.8: Memory write transaction for a store operation: movl %eax,A.

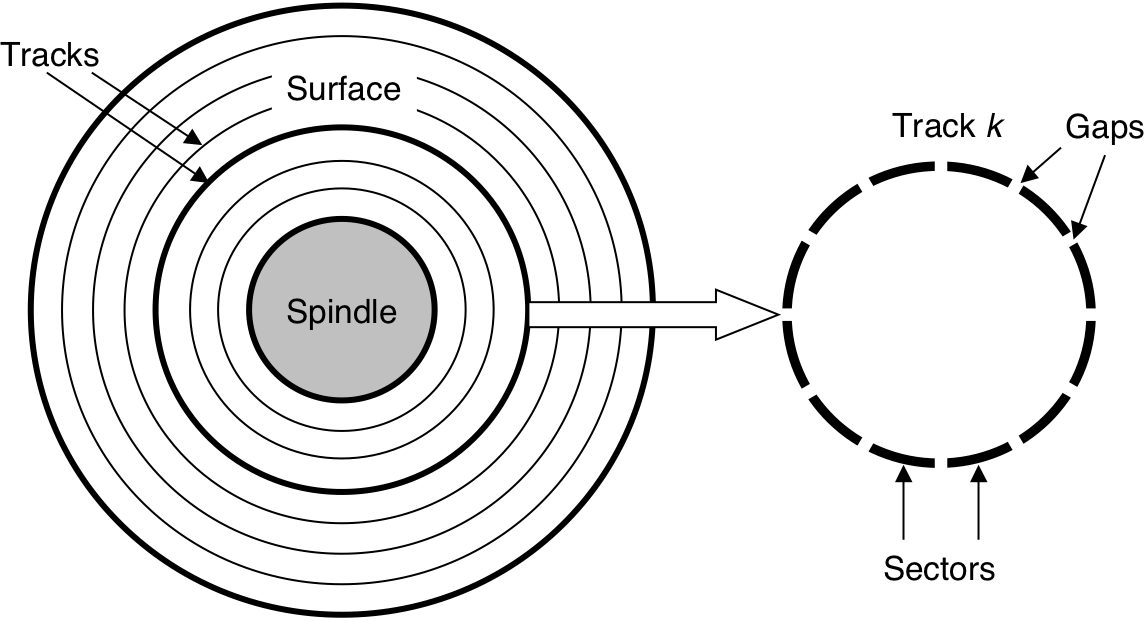

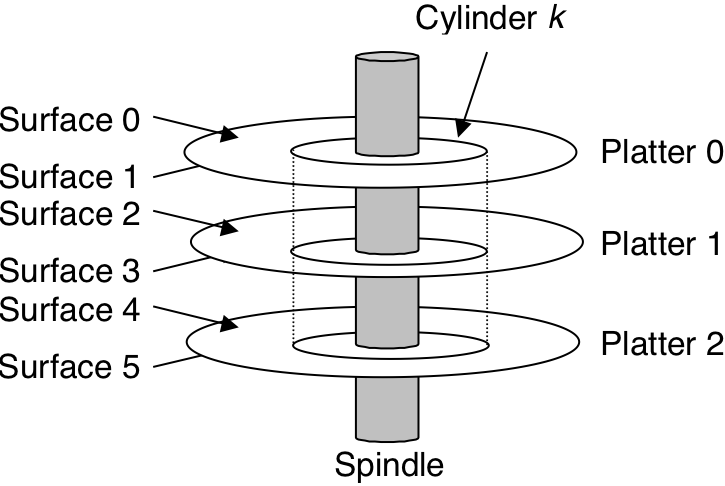

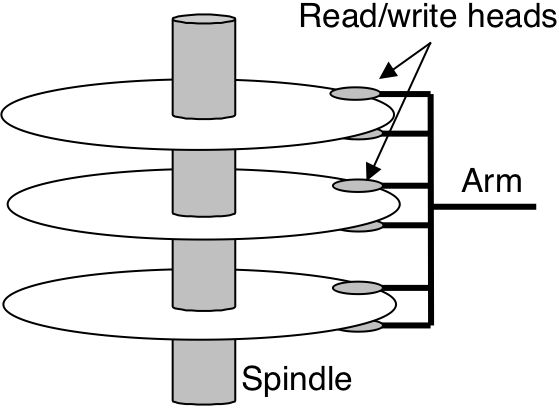

Figure 6.9: Disk geometry.

Figure 6.9: Disk geometry.

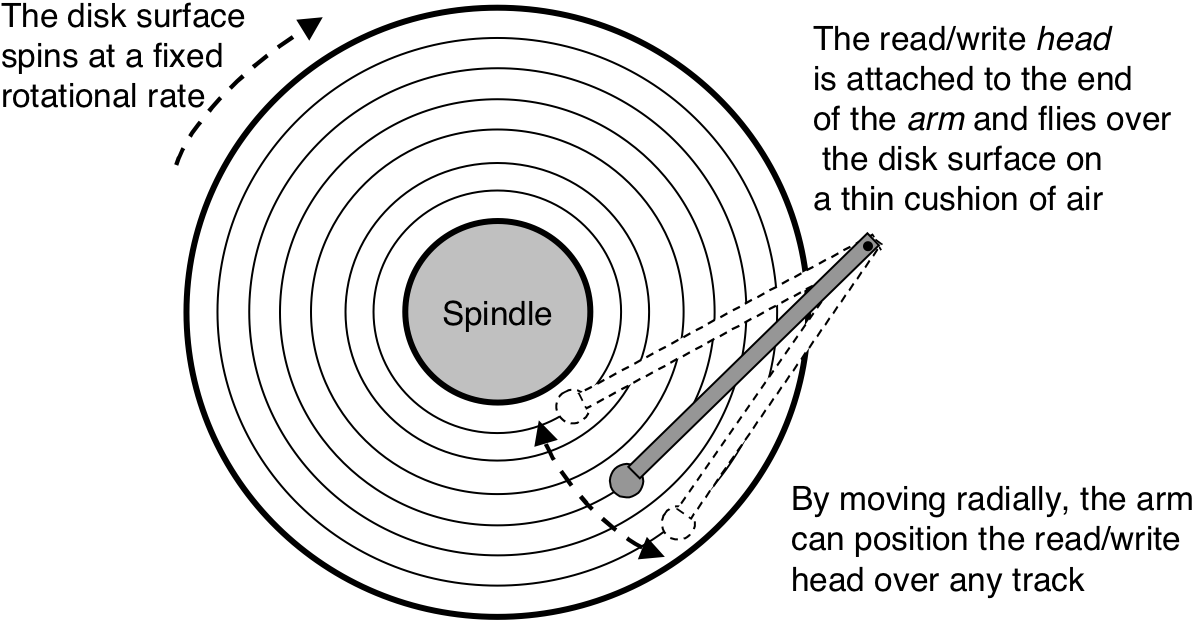

Figure 6.10: Disk dynamics.

Figure 6.10: Disk dynamics.

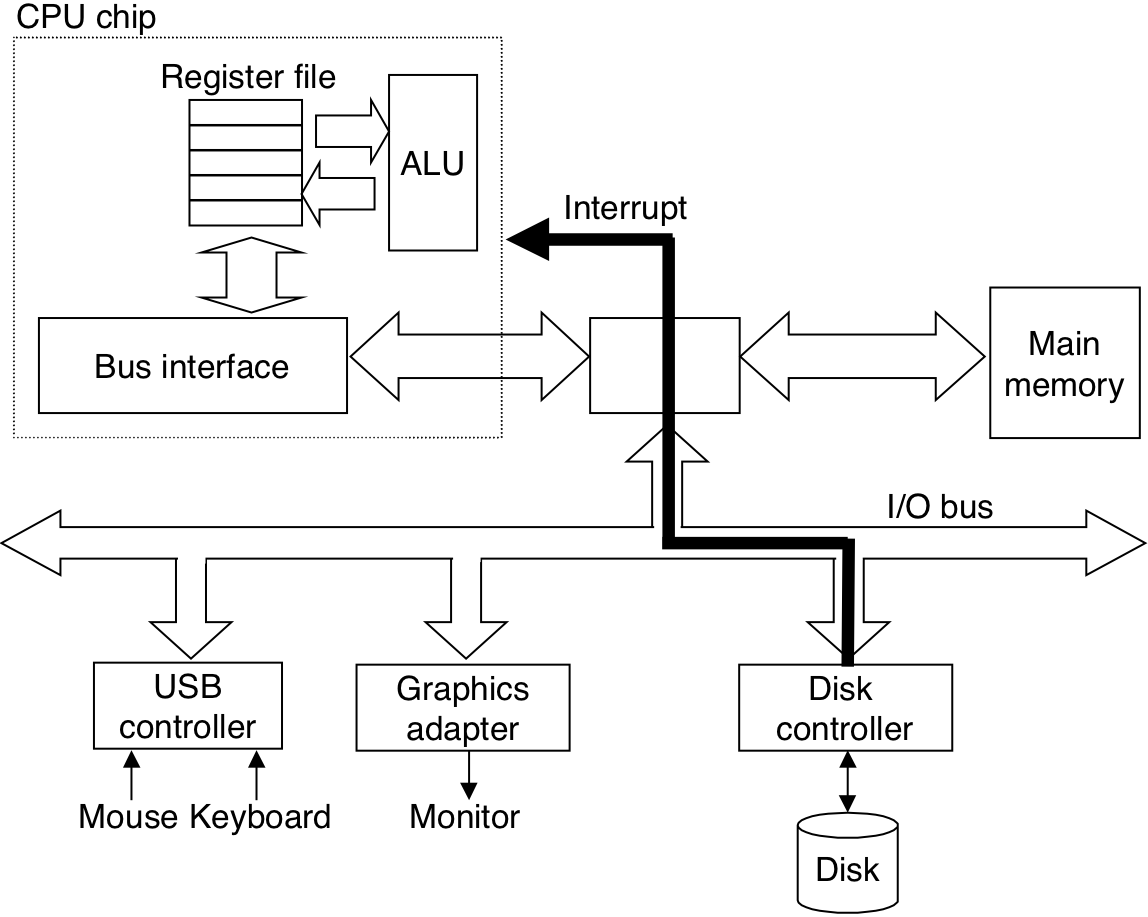

Figure 6.11: Typical bus structure that connects the CPU, main memory, and I/O devices.

Figure 6.12: Reading a disk sector.

Figure 6.12: Reading a disk sector.

Figure 6.12: Reading a disk sector.

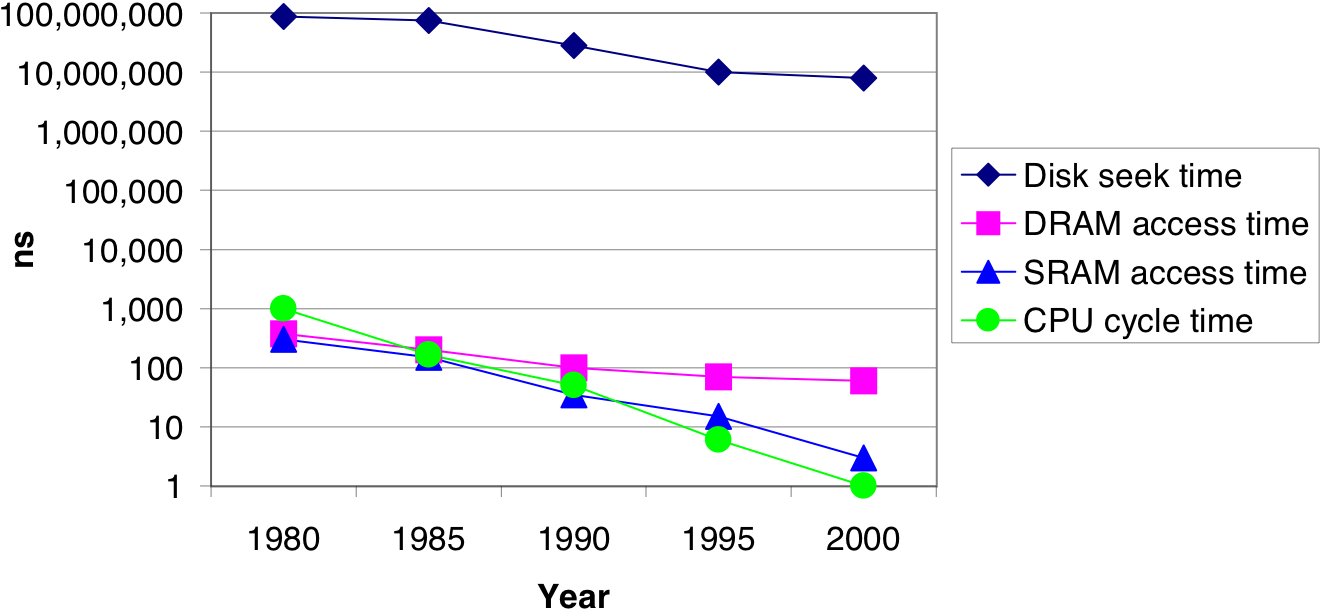

Figure 6.16: The increasing gap between DRAM, disk, and CPU speeds.

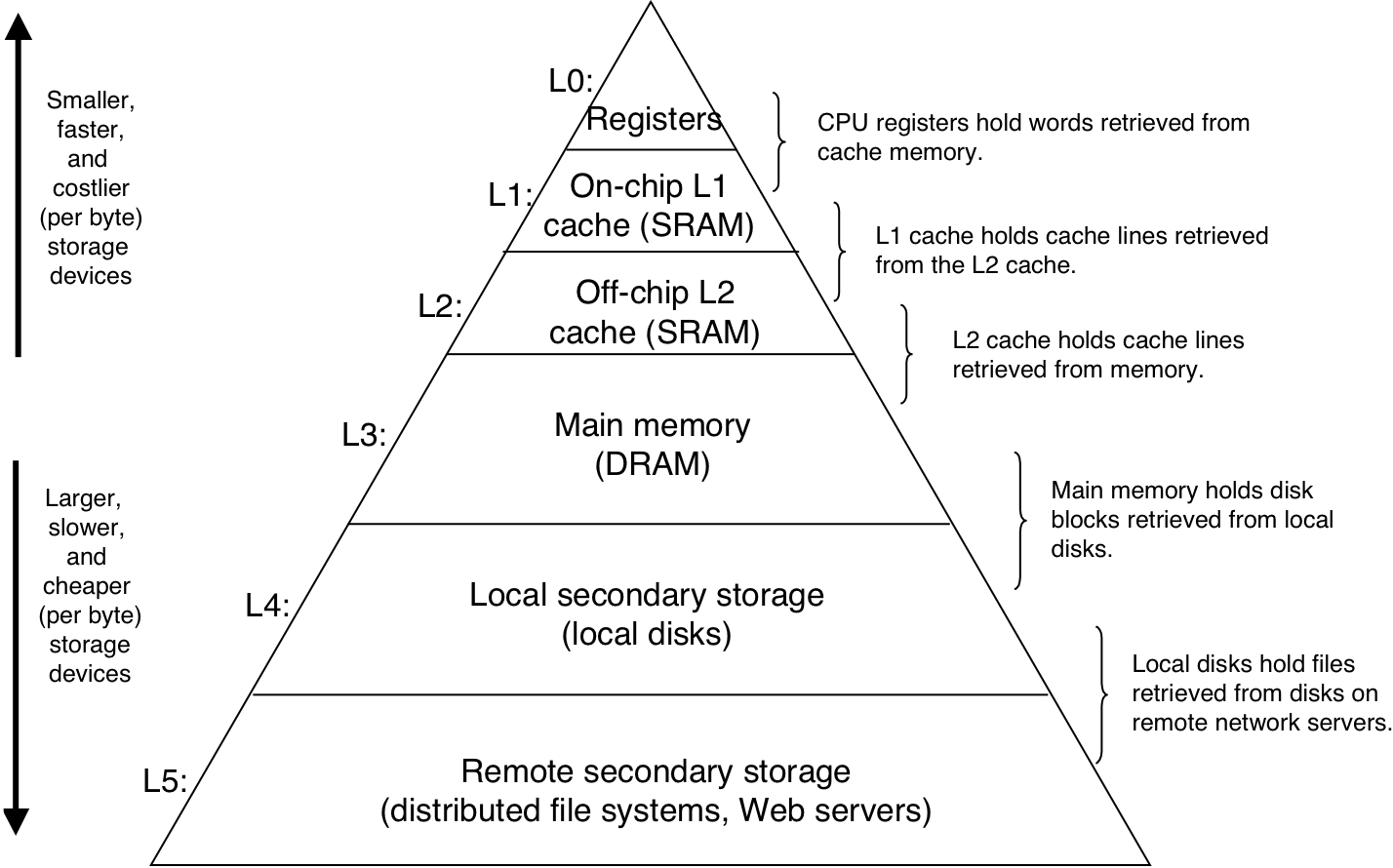

Figure 6.21: The memory hierarchy.

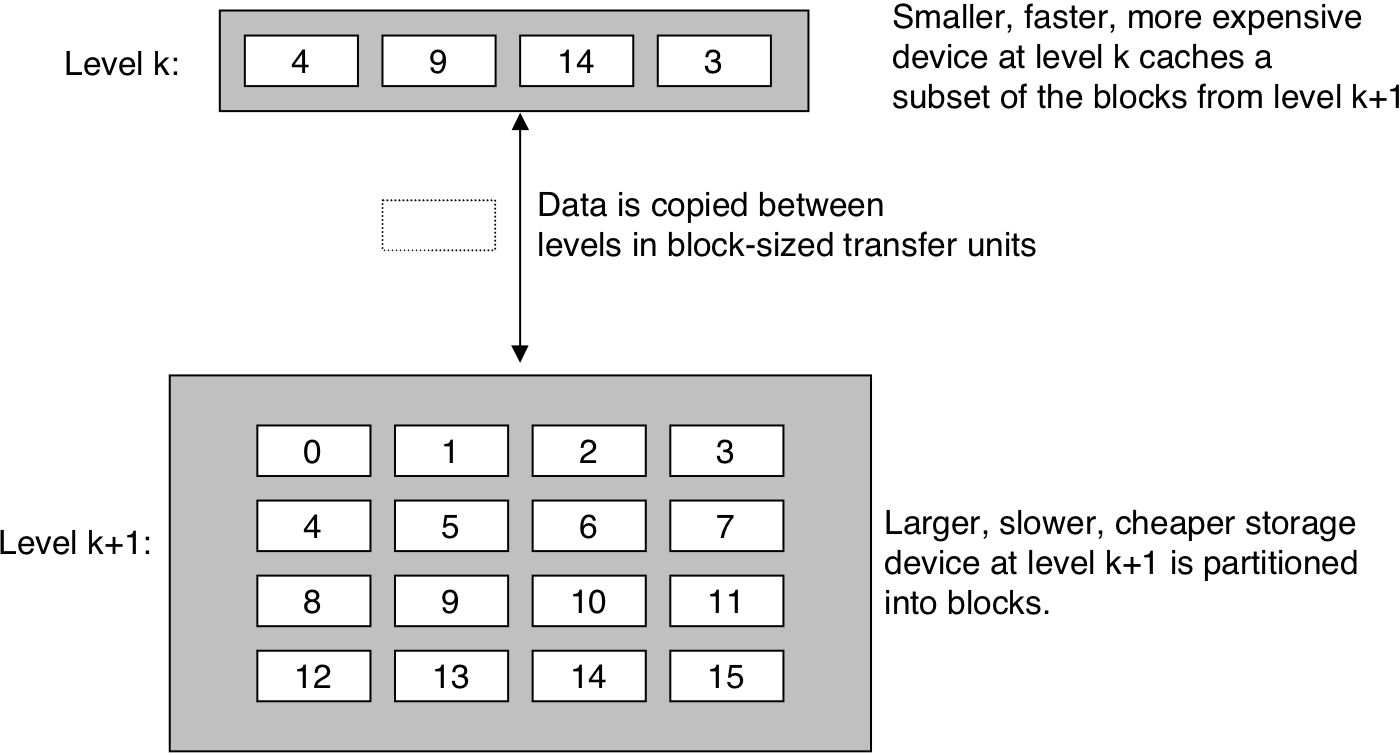

Figure 6.22: The basic principle of caching in a memory hierarchy.

Figure 6.24: Typical bus structure for L1 and L2 caches.

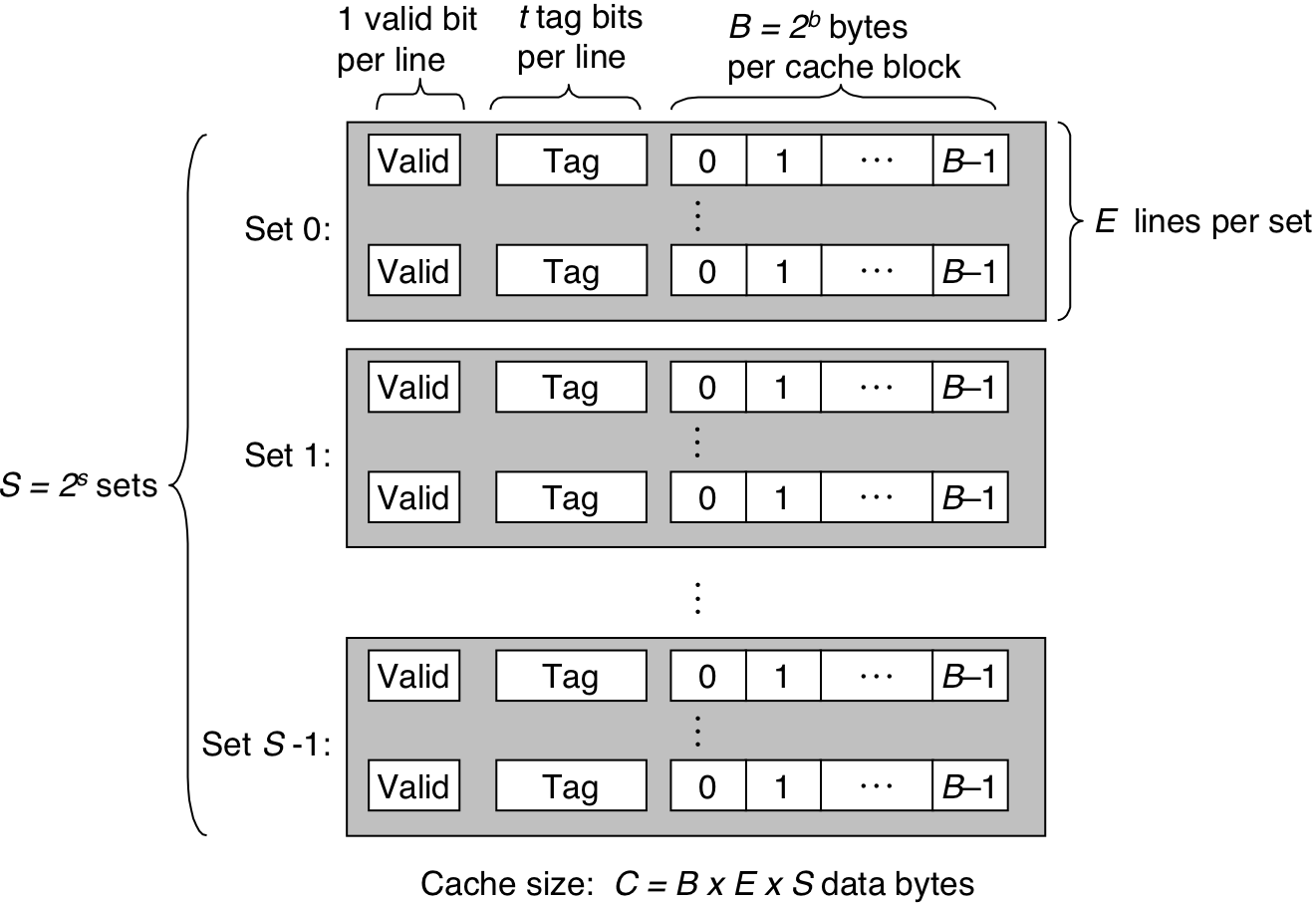

Figure 6.25: General organization of cache (S, E, B, m).

Figure 6.25: General organization of cache (S, E, B, m).

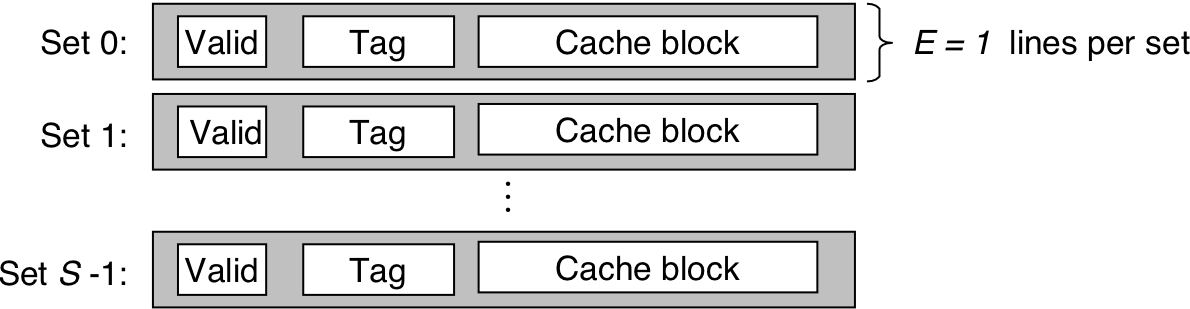

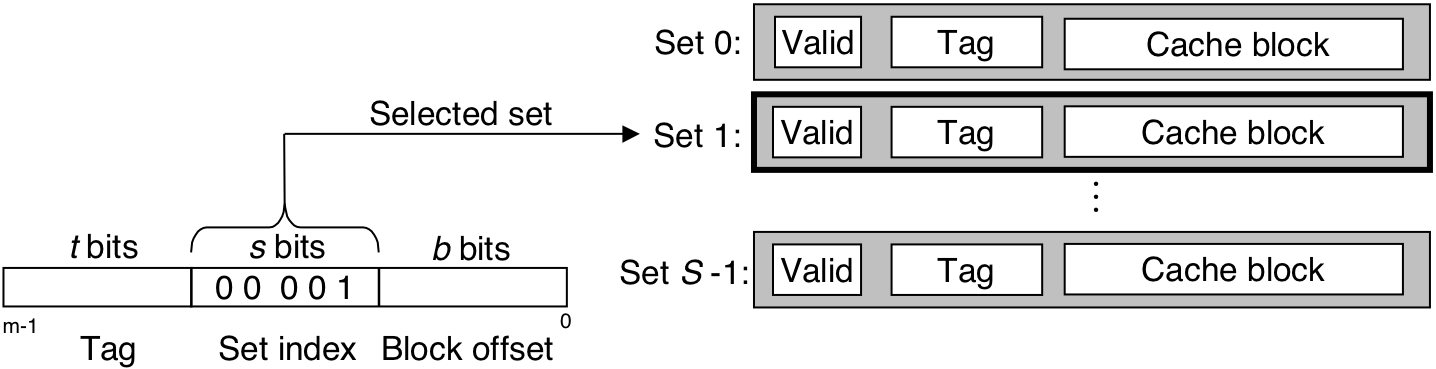

Figure 6.27: Direct-mapped cache (E = 1).

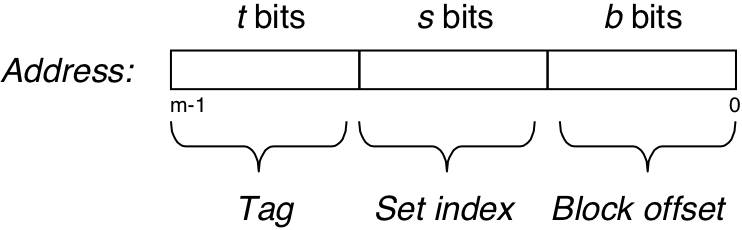

Figure 6.28: Set selection in a direct-mapped cache.

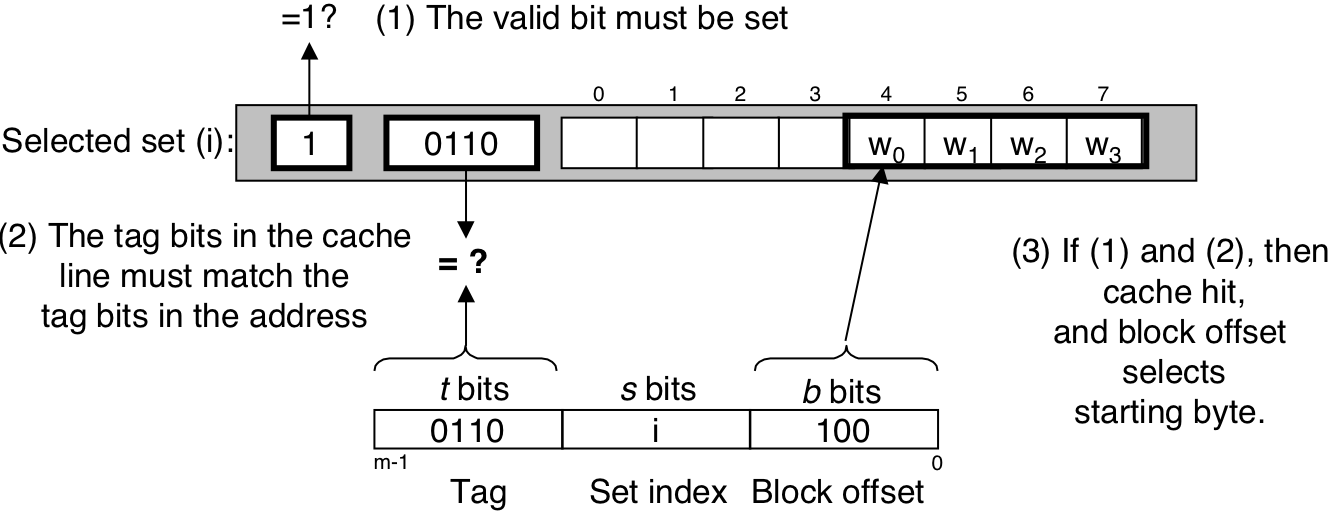

Figure 6.29: Line matching and word selection in a direct-mapped cache.

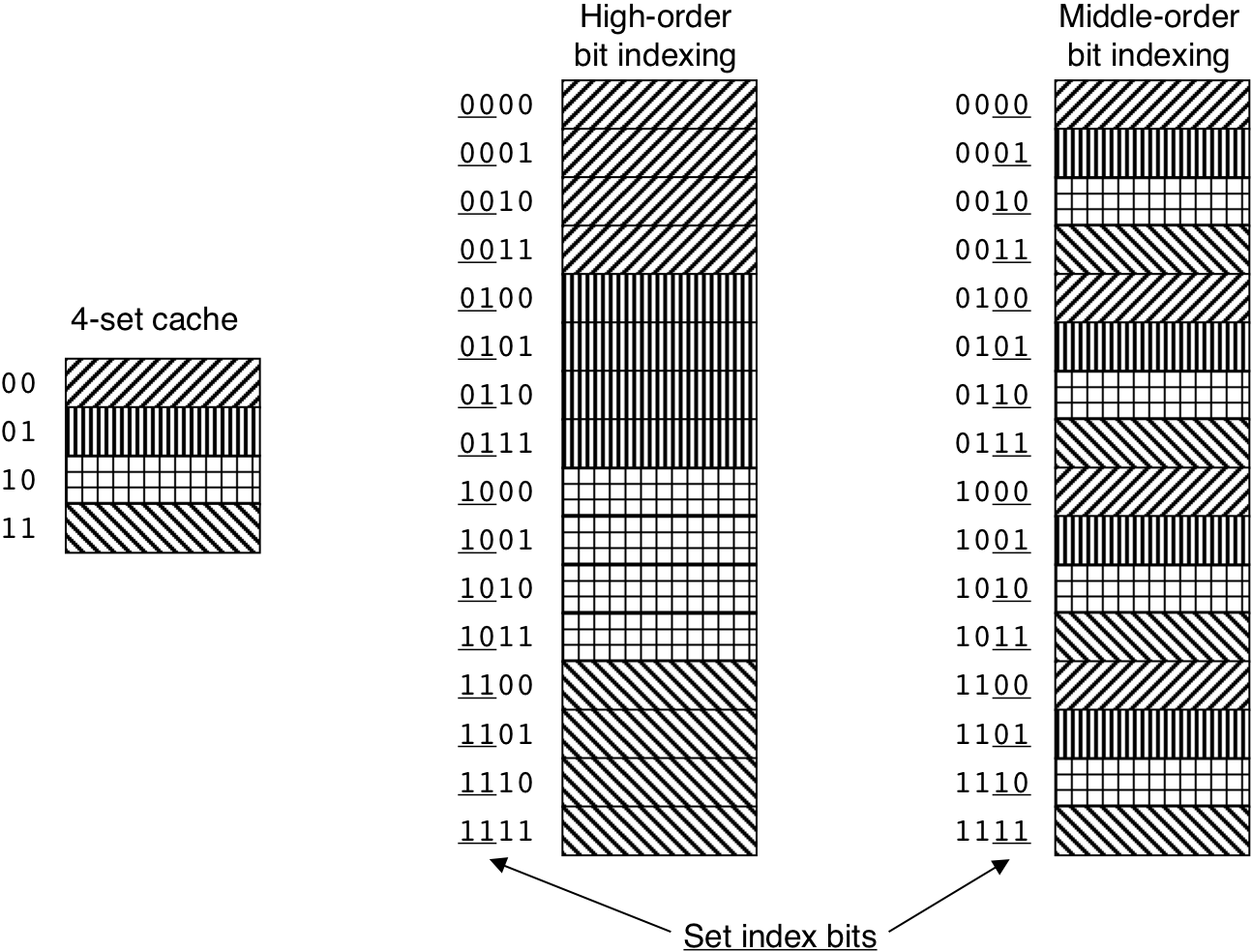

Figure 6.31: Why caches index with the middle bits.

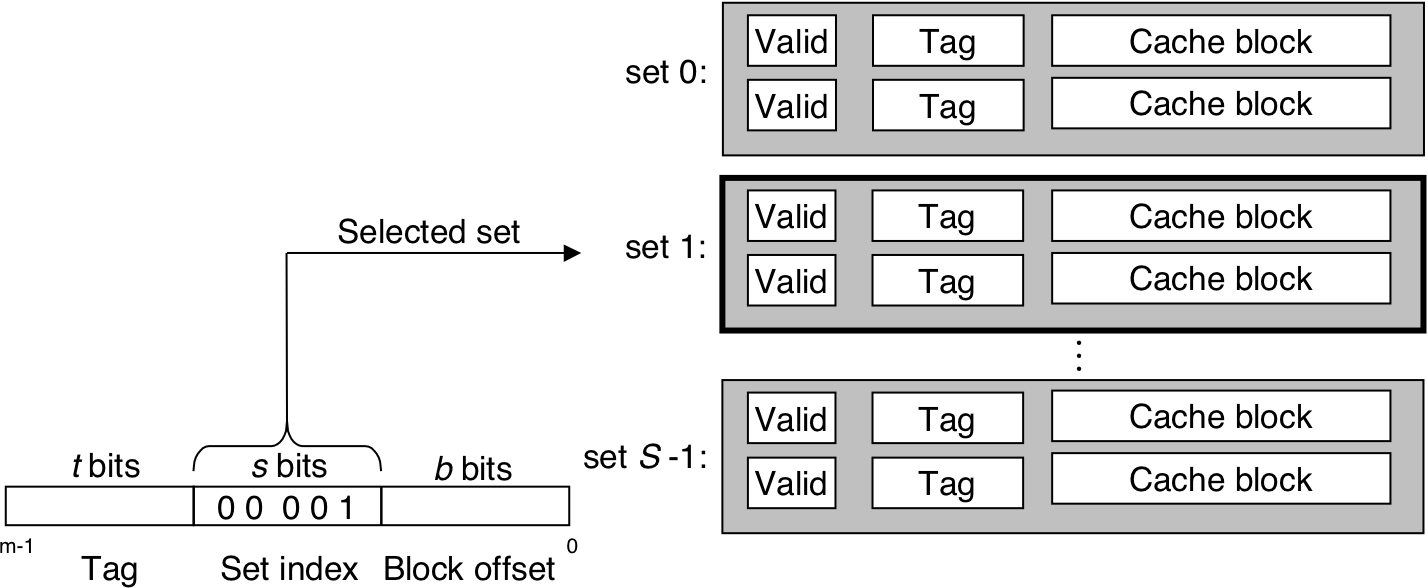

Figure 6.32: Set associative cache (1 < E < C/B).

Figure 6.33: Set selection in a set associative cache.

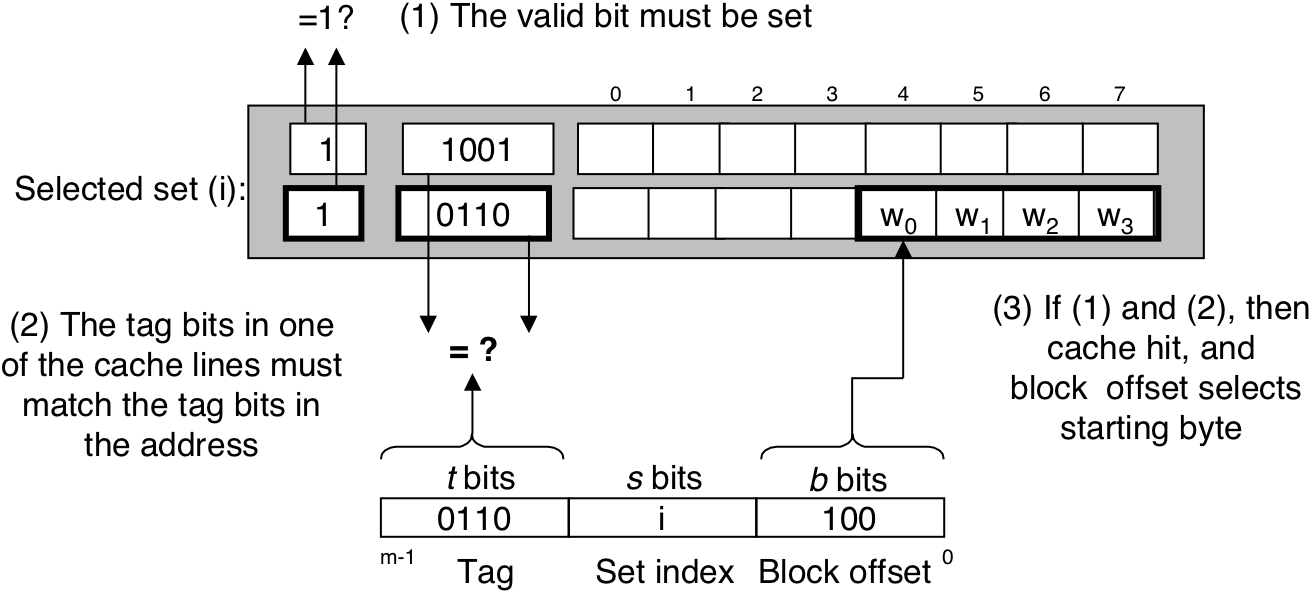

Figure 6.34: Line matching and word selection in a set associative cache.

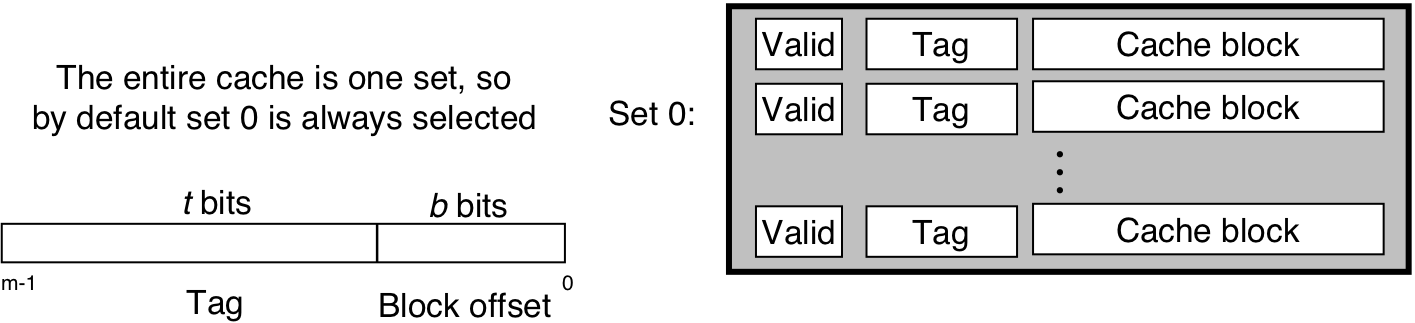

Figure 6.35: Fully set associative cache (E = C/B).

Figure 6.36: Set selection in a fully associative cache.

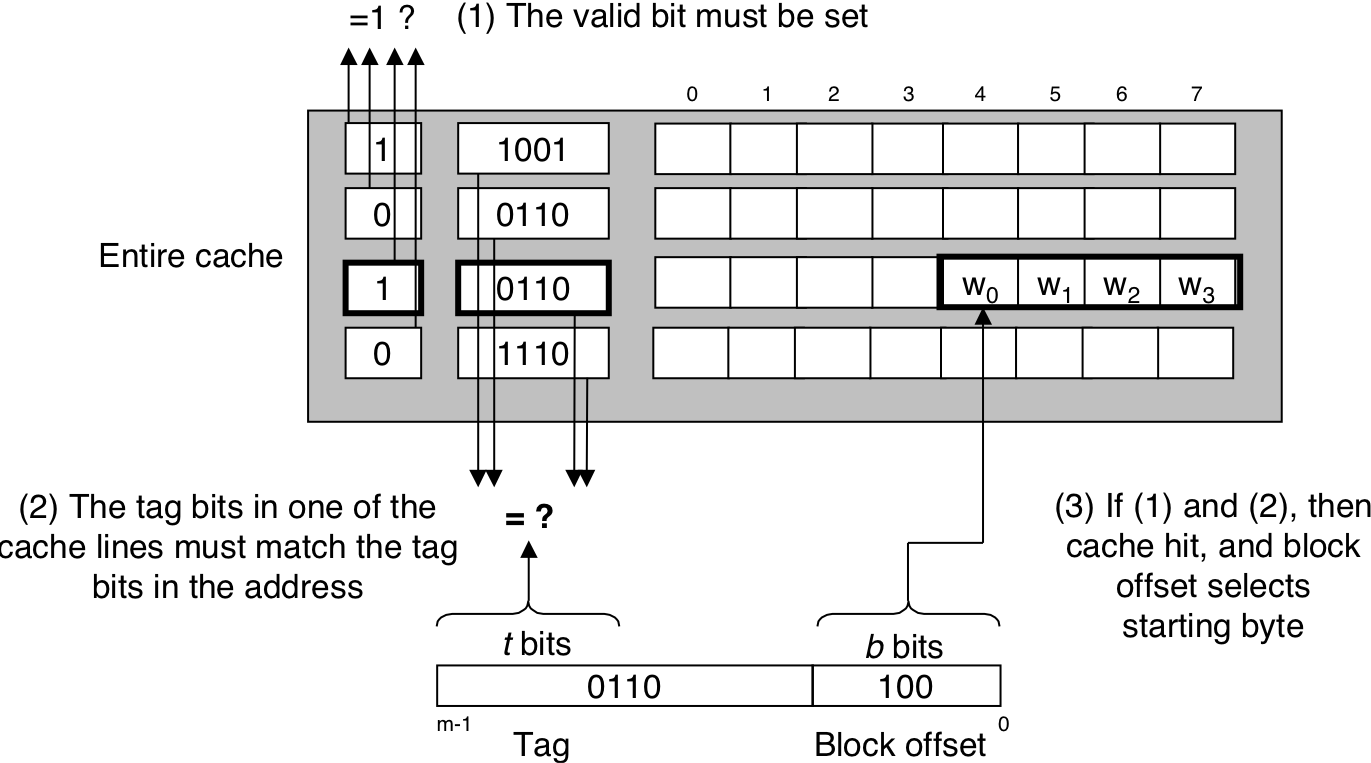

Figure 6.37: Line matching and word selection in a fully associative cache.

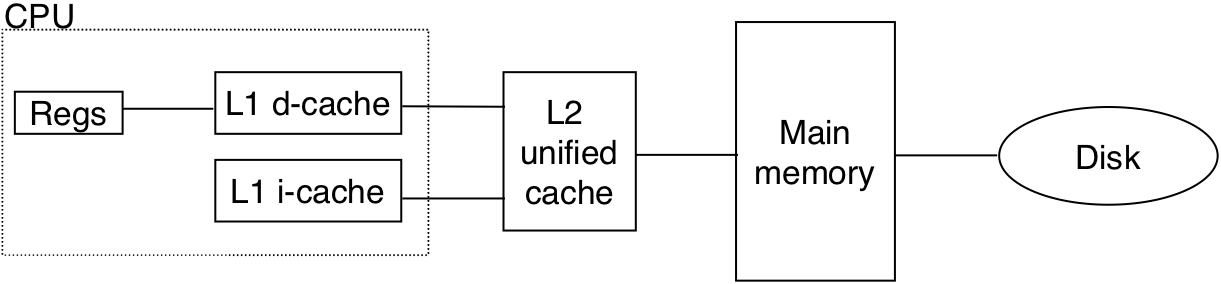

Figure 6.38: A typical multi-level cache organization.

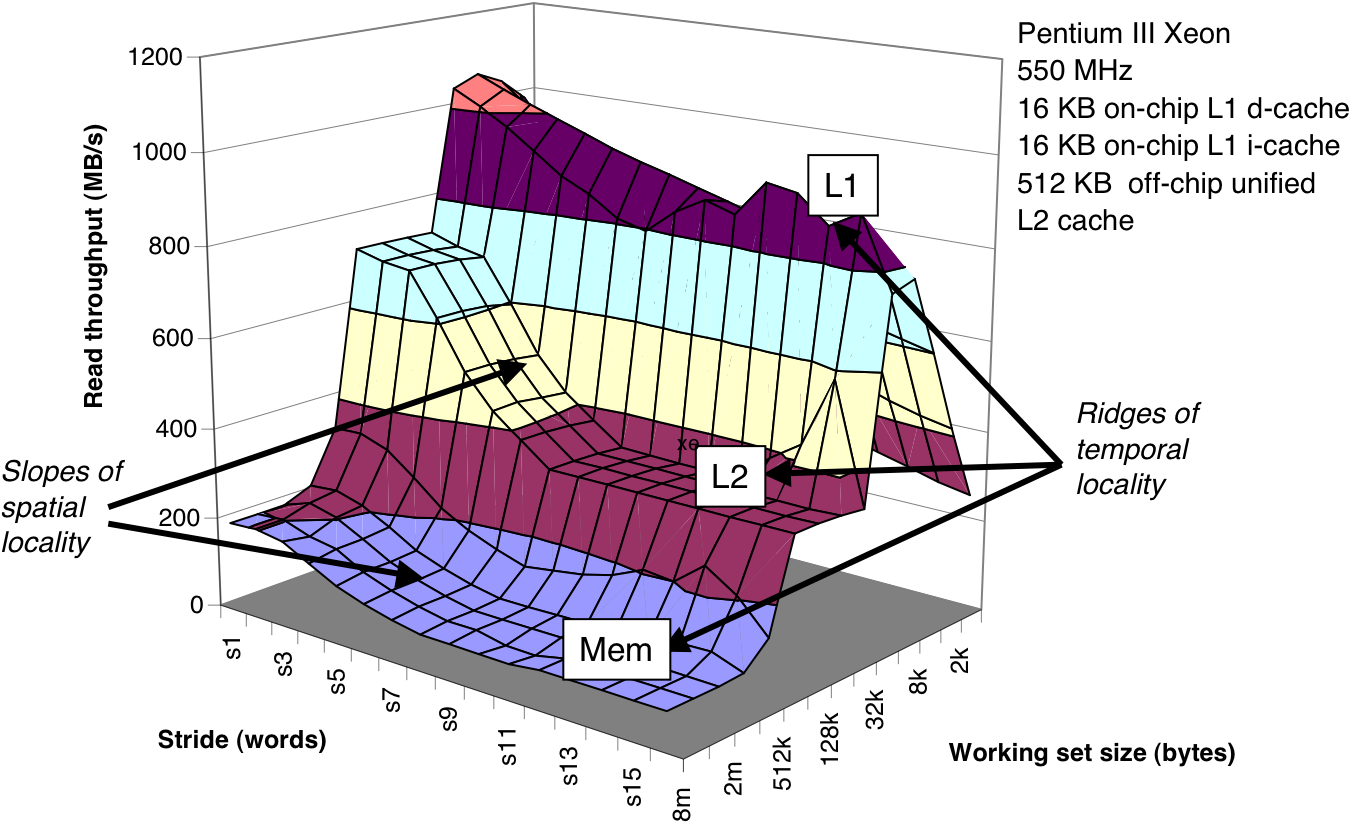

Figure 6.42: The memory mountain.

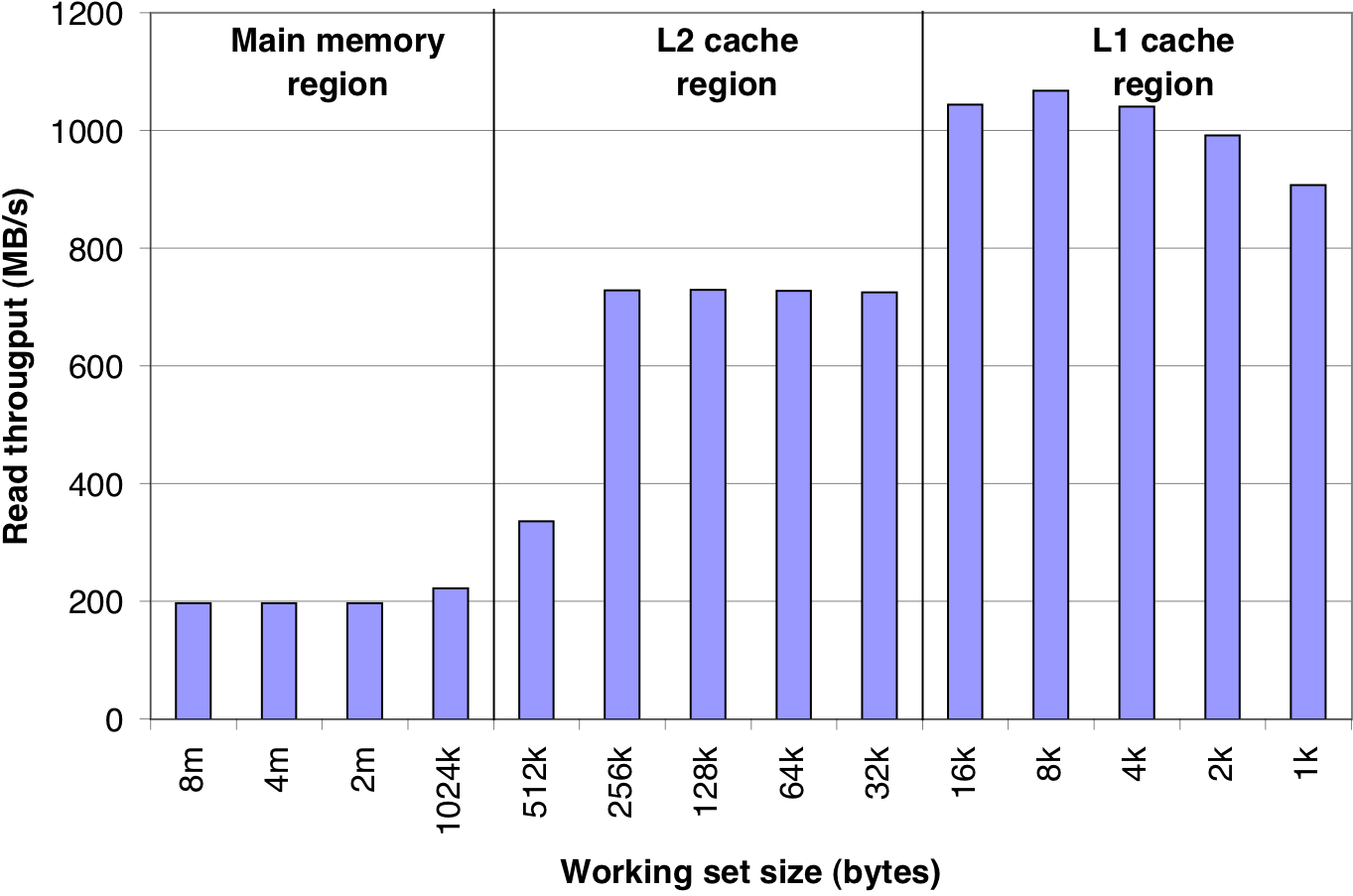

Figure 6.43: Ridges of temporal locality in the memory mountain.

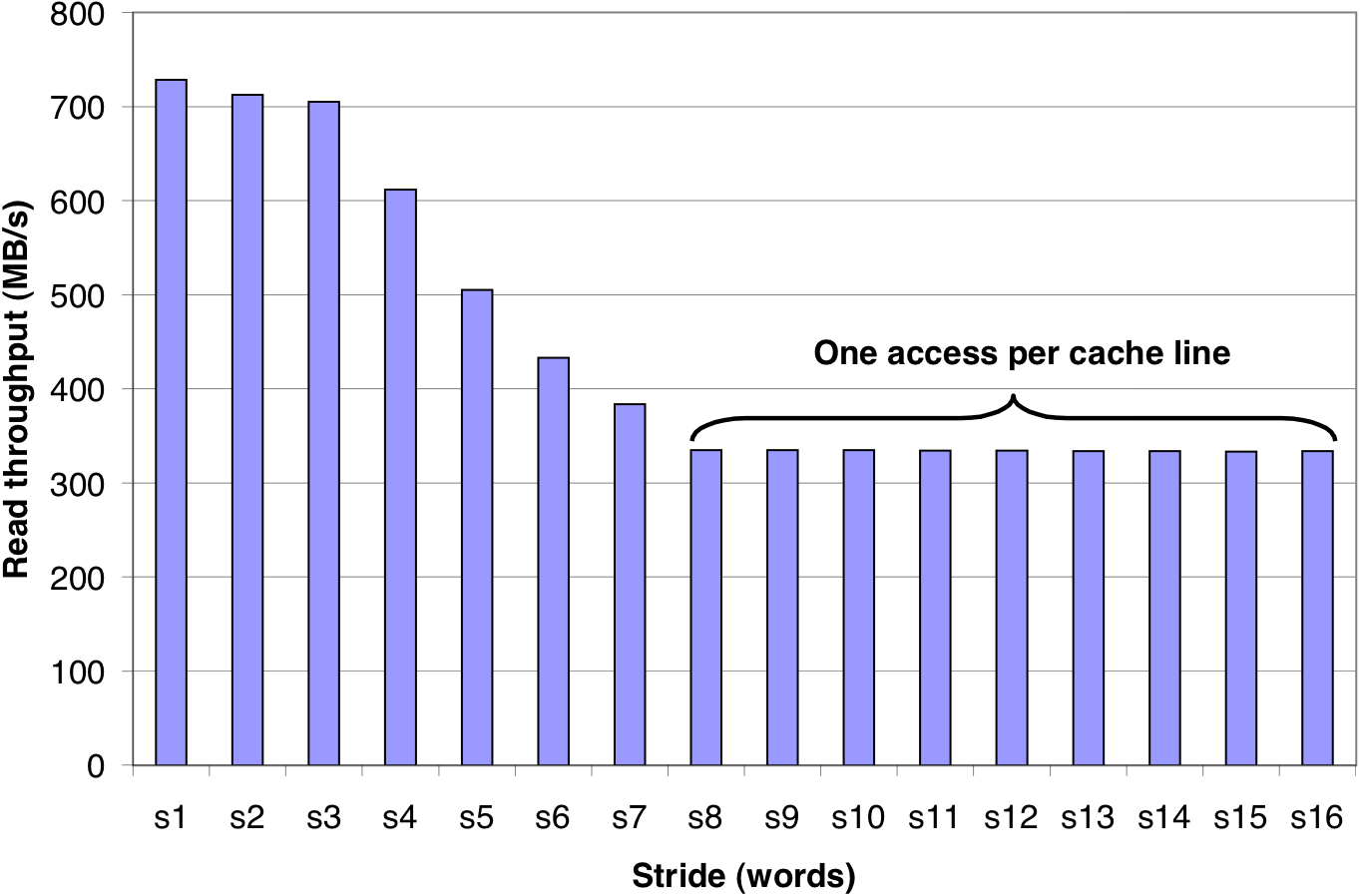

Figure 6.44: A slope of spatial locality.

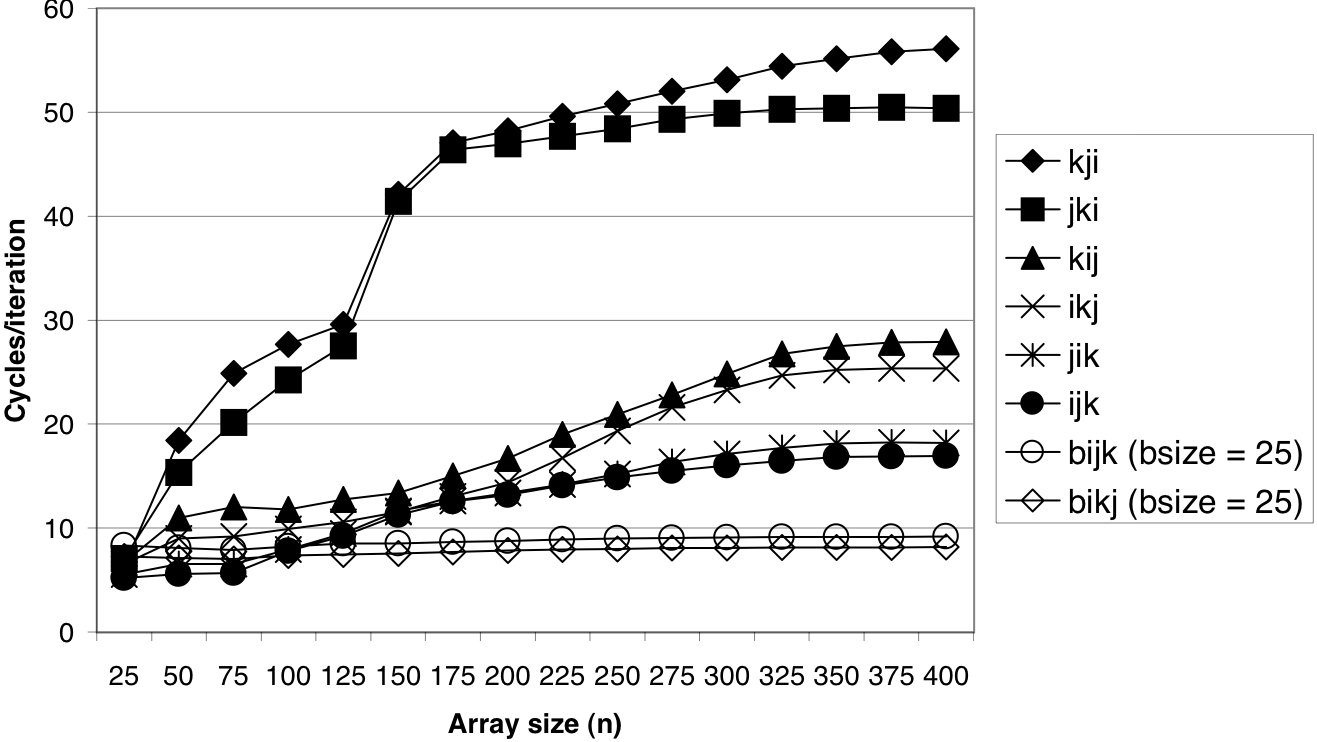

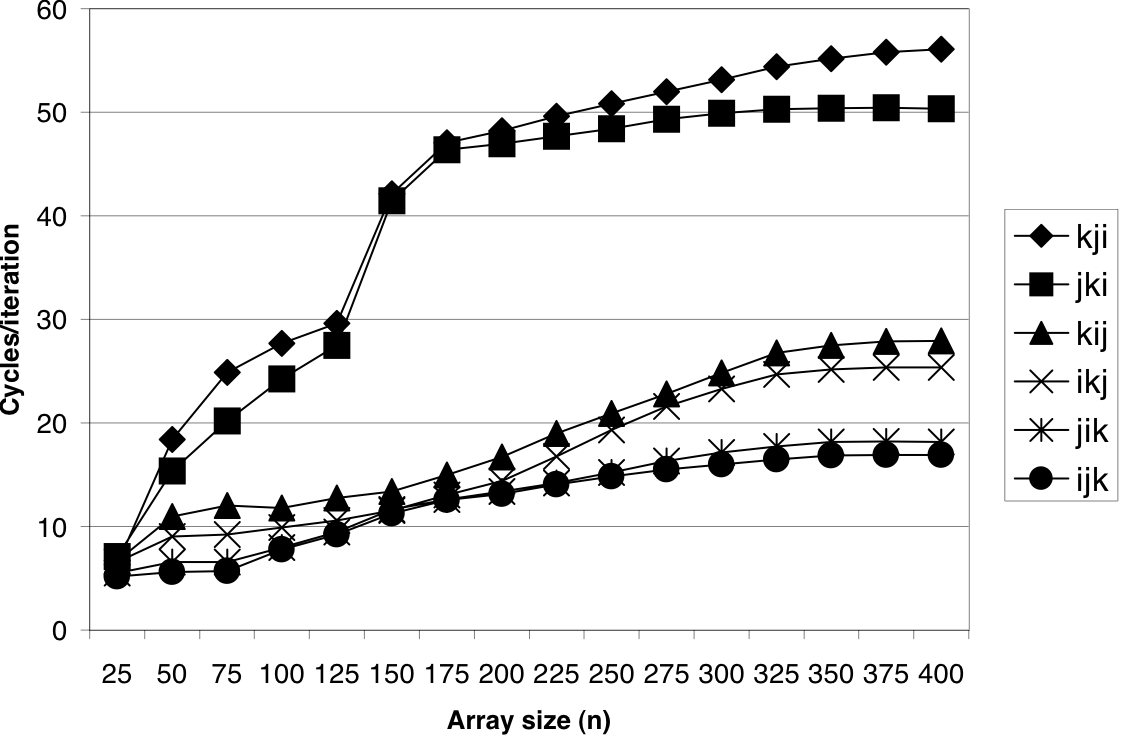

Figure 6.47: Pentium III Xeon matrix multiply performance.

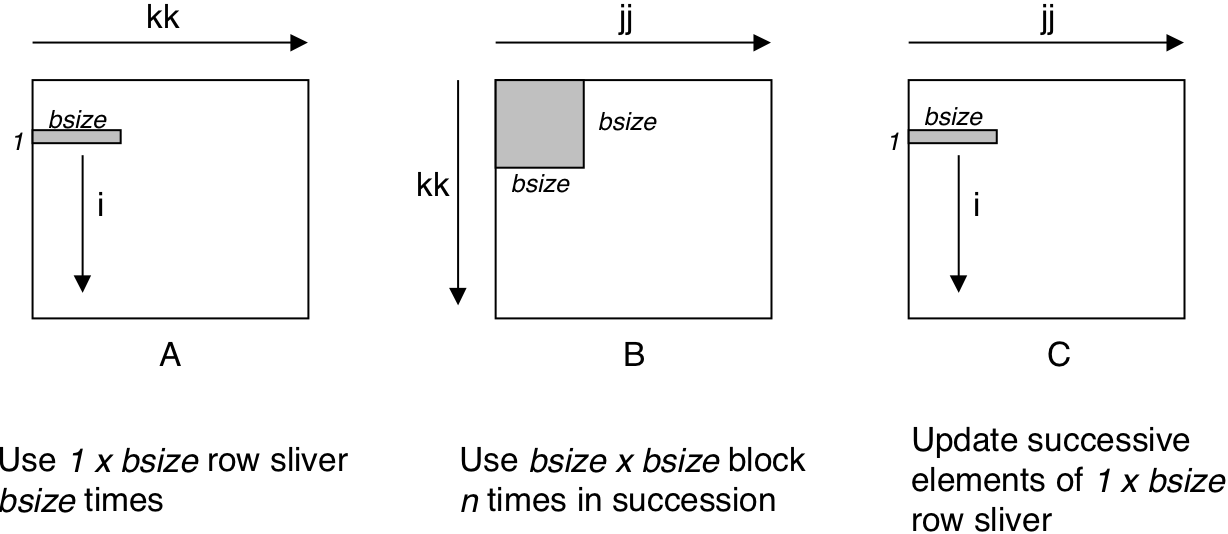

Figure 6.49: Graphical interpretation of blocked matrix multiply

Figure 6.50: Pentium III Xeon blocked matrix multiply performance.